本篇文章给大家谈谈coregen,以及coregency对应的知识点,希望对您有所帮助,不要忘了收藏本站喔。

本篇文章目录概览:

- 1、FPGA:ISE中如何使用DCM模块?

- 2、coregen.exe是什么进程

- 3、如何仿真IP核

- 4、CAD怎么建立一个双击就能改文字的块

- 5、什么是XCO、XAW文件——CoreGen文件概述

- 6、求助:关于C6416的EMIFA接FPGA进行数据传输的问题,FPGA作为FIFO,希望...

FPGA:ISE中如何使用DCM模块?

1、我新建立一个工程,然后点击New Source-IP core-FPGA features and Design-Clocking Wizard.这个步骤对吗?可是我的Clocking Wizard是灰色的,无法点击。那里面很多IP core都无法使用。

2、DCM的一般使用方法是,将其输出clk_1x接在BUFG的输入引脚上,BUFG的输出引脚反馈回来接在DCM的反馈时钟脚CLKFB上。另外,在FPGA里,只有BUFG的输出引脚接在时钟网络上,所以一般来说你可以不使用DCM,但你一定会使用BUFG。

3、最后,还可以使用DCM将输入时钟信号转换为差分I/O标准信号。例如,DCM可以将输入的LVTTL时钟信号转换为LVDS时钟信号发送出去。

coregen.exe是什么进程

1、这是一个无威胁文件。属于Microsoft Corporation的文件。

2、agent.exe是Dell电脑提供的用户监视和管理系统的程序。这不是一个重要的进程。禁用它可以节省用户资源。注意:agent.exe也可能是ForteAgentNewsgroupReader新闻组阅读器。agentsvr.exe是一个ActiveX插件,用于多媒体程序。

3、病毒!我哥哥在电脑精英公司工作,他说逗号加句号的就是病毒!病毒进程一般不能和普通进程同名,所以他们一般都加上一些小的伪装。

4、guard.exe是ewido的守护进程,是保护ewido.exe这个进程不被恶意软件关闭的,关了它就等于关了ewido的守护 ewido,即Ewido Security Suite Plus,是一种优秀的反木马程序。

5、直译过来就是:英雄联盟的核心可执行程序 用于英雄联盟客户端的游戏更新和记录等。

6、Conhost.exe进程是微软为其Vista以及WinWindows 2008(服务器版)系统定义的系统文件,在系统中被称为“控制台窗口主机”。

如何仿真IP核

1、首先需要将.bdf原理图文件转换为Verilog HDL等第三方EDA工具所支持的标准描述文件。

2、ModelSim可以直接编译和添加Xilinx的库,目前的ise中(在开始菜单xilinx工具下找吧)直接有使用ModelSim编译库的工具。

3、ISE 的库(要确保 Process属性窗口中“Target Simulator”正确设置为“Modelsim SE”,如图附 2);编译好的库放在$Xilinx/Verilog/mti_se/ 下(在 modelsim中仿真 ip 核需添加库时指向该路径即可,如图附 3)。

4、如果以前ModelSim工程里也有调用过xilinx里定制的IP核没出错的话,那就你删除了上面说的文件引起的。

CAD怎么建立一个双击就能改文字的块

用可编辑属性。把1和块一起在组成一个块,双击就可以编辑文字。

首先,打开AutoCAD并绘制形状,如下图所示,然后进入下一步。其次,完成上述步骤后,在命令行中输入ATT,然后按空格键打开属性定义框。

这个叫属性块,与一般块相比,属性块要先定义属性,定义块时,把它一起包含进来,并设置好类型。这样在双击是会弹出属性编辑成对话框供你修改。

首先在电脑里打开CAD软件,然后从图中找到文字并进行双击,问题显示为双击无法进入到编辑状态,如下图所示。这时通过op命令进入到选项窗口,如下图所示。通过选择选项窗口下用户系统配置选项卡,如下图所示。

首先,我们从图中找到文本并双击它,问题是双击不能进入编辑状态。通过op命令进入选项窗口。选择选项窗口下的用户系统配置选项卡。双击编辑窗口标准操作项目并检查它们。点击应用程序并确认。

先把图框绘制好,写好固定文字(工程名称、设计、审核等等)。命令【att】,依次写入常编辑的文字。在【模式】里勾选【预置】(插.入图块时不在命令行提示),【文字对正】保持默认【左】。命令【w】写入块。

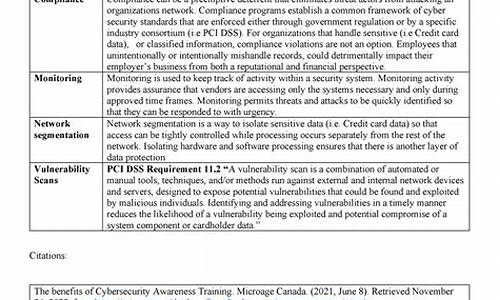

什么是XCO、XAW文件——CoreGen文件概述

1、XAW文件:是一个二进制文件,是使用CoreGen产生Core时一系列输出文件中的一个,里面存放了使用“architecture Wizard”产生core时所设置的参数。当重新定制该core时,XAW文件可以作为一个输入文件提示原来的设置。

2、XCO文件,是使用CoreGen产生Core时一系列输出文件中的一个,里面存放了产生core时所需的参数。当重新定制该core时,XCO文件可以作为一个输入文件提示原来的设置。

求助:关于C6416的EMIFA接FPGA进行数据传输的问题,FPGA作为FIFO,希望...

1、EMIFA的数据线是固定的,CE0~CE3都可以用,你DSP操作空间对应的地址就从那个空间的首地址地区FIFO数据,这是肯定的。我用的是6713,跟你这个差不多。

2、在内存和外设接口(EMIFA接口、EMIFB接口、HPI或PCI接口、McBSP串口、UTOPIA接口等)之间所有的数据传输都由EDMA来处理。

3、你应该是指异步的ram或者fifo吧 如果写时钟大于读时钟,并且写使能一直为1‘ 的话,是会溢出的,事实上当FLAG信号’FULL‘为1时,接下来的写数据就会被抛弃。

关于coregen和coregency的介绍到此就结束了,不知道您从中找到你需要的信息了吗 ?如果您还想了解更多这方面的信息,记得收藏关注本站。